Как использовать память EDO, в системах не поддерживающих данный вид памяти!

На сегодняшний день в России самый большой парк компьютеров на базе 486-х процессоров. И, несмотря на то, что они технически и морально устарели их ещё можно использовать как для набора текста так и в качестве дежурного компьютера по приёму электронной почты. Известны многие способы повышения производительности. Но в основном все они были направлены на повышение системных частот. О добавлении памяти разговоров было меньше, так как она являлась наиболее дорогим удовольствием при комплектации. Почти все материнские платы, поколения 486-х процессоров, имели возможность установки только памяти FPM (72 pin), а в то время уже началось шествие памяти EDO - несовместимого по протоколу работы с FPM. Системный чипсет мог поддерживать как минимум до 64 мегабайт. Но чтобы найти такой модуль FPM надо было приложить немало усилий а также финансовых средств. Поэтому типичная конфигурация 486-х машин - 16 мегабайт. Вскоре вместе с 486-ми системами с рынка ушли и модули памяти FPM. Теперь пополнить объём памяти стало ещё труднее. Однако память EDO ещё можно встретить в продаже. Предлагаю Вам, доработку модулей памяти EDO, для преобразования их в модули памяти FPM. Компьютер на базе процессора AMD486DX4-132 (не путать с DX5)с частотой внешней шины 66МГц и устройствами VLB, а также объёмом памяти в 64 мегабайта может составить серьёзную конкуренцию первым системам на базе Pentium с шиной PCI.

Немного теории:

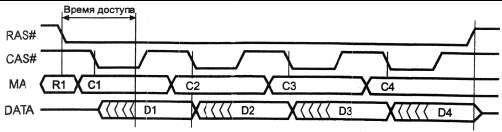

Запоминающие ячейки микросхем DRAM организованы в виде двумерной матрицы. Адрес строки и столбца передаётся по мультиплексированной шине адреса MA (Multiplexed Address) и стробируется по спаду импульсов RAS# (Row Access Strobe) и CAS# (Column Access Strobe). Временная диаграмма "классических" циклов записи и чтения приведена на рисунке 1.

Рисунок 1. Временные диаграммы чтения и записи динамической памяти

Поскольку обращения (запись или чтение) к различным ячейкам памяти обычно происходят в случайном порядке, то для поддержания сохранности данных применяется регенерация (Memory Refresh — «освежение» памяти) — регулярный циклический перебор ее ячеек (обращение к ним) с холостыми циклами. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. Максимальный период обращения к каждой строке Trf (refresh time) для гарантированного сохранения информации у современной памяти лежит в пределах 8-64 мс. В зависимости от объема и организации матрицы для однократной регенерации всего объема требуется 512, 1024, 2048 или 4096 циклов обращений. Временная диаграмма, приведенная на рисунке 1, может быть модифицирована для случая последовательного обращения к ячейкам, принадлежащим к одной строке матрицы. В этом случае адрес строки выставляется на шине только один раз и сигнал RAS# удерживается на низком уровне на время всех последующих циклов обращений, которые могут быть как циклами записи, так и чтения. Такой режим обращения называется режимом быстрого страничного обмена FPM (Fast Page Mode), иногда просто Page Mode, его временная диаграмма приведена на рисунке 2. Понятие «страница» на самом деле относится к строке (row), а состояние с низким уровнем сигнала RAS# называется «открытой страницей». Преимущество данного режима заключается в экономии времени за счет исключения фазы выдачи адреса строки из циклов, следующих за первым, что позволяет повысить производительность памяти. Для памяти с временем доступа 60 не время цикла обмена внутри страницы может быть сокращено до 35 нc.

Рисунок 2. Страничный режим считывания стандартной DRAM (FPM).

Способность работать в режиме FPM является «заслугой» не микросхем или модулей памяти (в этом режиме способны работать и самые «древние» микросхемы, и микросхемы EDO, о которых речь пойдет ниже), а контроллера динамической памяти (то есть чипсета). Однако по сложившейся терминологии обозначение FPM относят к «стандартным» микросхемам и модулям динамической памяти, которые не являются EDO, BEDO или SDRAM. Иногда их все-таки более точно называют стандартными (Std). Преимуществами FPM позволяет воспользоваться конвейерная адресация, применяемая в процессорах, начиная с 80286.Обратим внимание на то, что информация на выходе микросхем стандартной DRAM появляется с некоторой задержкой относительно спада импульса CAS# и держится только во время его низкого уровня. После подъема CAS# выходной буфер микросхемы переводится в третье (высокоимпедансное) состояние. Стандартная память со временем доступа 60-70 нc в режиме быстрого страничного обмена при частоте системной шины 66 МГц может обеспечить лучший пакетный цикл чтения 5~3~3~3.

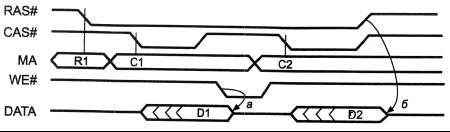

Следующей модификацией памяти, направленной на повышение производительности при том же быстродействии запоминающих элементов, явилась память EDO (Extended или Enhanced Data Out) DRAM. Эта память содержит регистр-защелку (data latch) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении. Регистр «прозрачен» при низком уровне сигнала CAS#, а по его подъему фиксирует текущее значение выходных данных до следующего его спада. Перевести выходные буферы в высокоимпедансное состояние можно либо подъемом сигнала ОЕ# (Output Enable), либо одновременным подъемом сигналов CAS# и RAS#, либо импульсом WE#, который при высоком уровне CAS# не вызывает записи (в PC управление по входу ОЕ# практически не используют). Временная диаграмма работы с EDO-памятью в режиме страничного обмена приведена на рисунке 3, этот режим иногда называют гиперстраничным режи-мом обмена НРМ (Hyper Page mode). Его отличие от стандартного заключается в подъеме импульса CAS# до появления действительных данных на выходе мик-росхемы. Считывание выходных данных может производиться внешними схемами вплоть до спада следующего импульса CAS#, что позволяет экономить время за счет сокращения длительности импульса CAS#.

Рисунок 3. Страничный режим считывания EDO DRAM (HPM).

Время цикла внутри страницы для памяти со временем доступа 60 нс уменьшается с 35 нс (28,5 МГц) у стан-дартной DRAM до 25 нс (40 МГц) у EDO, повышая производительность в страничном режиме на 40%. EDO-память со временем доступа 60-70 нс в режиме гиперстраничного обмена при частоте системной шины 66 МГц может обеспечить лучший пакетный цикл чтения 5-2-2-2. Благодаря простоте данного усовершенствования при одном и том же времени доступа запоминающих элементов цена EDO-памяти почти не отличается от цены стандартной памяти. Однако ее применение дает эффект, соизмеримый с эффектом от установки стандартного асинхронного внешнего кэша. Более того, установка такого кэша в систему с EDO-памятью практически не дает повышения производительности. В результате распространилось мнение, что в EDO-памяти содержится внутренний кэш, однако для простого регистра-защелки название «кэш» звучит слишком торжественно.

Рисунок 4. Управление буфером EDO DRAM.

Микросхемы EDO DRAM применяются в современных SIMM-72 и DIMM-модулях, эти модули конструктивно и по назначению выводов совместимы со стандартными (FPM). Все EDO-модули не имеют бит паритета (однобитные микросхемы EDO не выпускаются). Контрольные разряды 36-битных EDO-модулей могут использоваться только в ЕСС-памяти, в которой доступ осуществляется всегда сразу ко всем байтам. Установка EDO DRAM вместо стандартной в неприспособленные для этого системы может вызвать конфликты выходных буферов устройств, разделяющих с памятью общую шину данных. Скорее всего этот конфликт возникнет с соседним банком памяти при использовании чередования (Bank Interleaving). Для отключения выходных буферов EDO-памяти внутри страничного цикла обычно используют сигнал WE#, не вызывающий записи во время неактивной фазы CAS# (рисунок 4, кривая а). По окончании цикла буферы отключаются лишь по снятию сигнала RAS# (рисунок 4, кривая б).

F

Собственно перейдём к практике. Необходимо собрать схему представленную на рисунке 5. Сигналы CASL# и CASH# берём от выводов микросхем на одной из сторон модуля (распайку можно посмотреть здесь). Выходной сигнал OE# будет непосредственно управлять высокоимпедансным состоянием микросхемы; его необходимо подключить к сигналу OE# микросхемы. При этом ножку данной микросхемы необходимо отпаять от платы, приподняв краем лезвия (для микросхем поверхностного монтажа). Данная схема состоит из двух буферных усилителей и логического элемента "ИЛИ". Эти функции выполняют микросхемы ТТЛ-логики АП5 и ЛИ1. По возможности необходимо использовать серию 1531, но можно и 1533 (всё зависит от быстродействия вашей системы). Отечественные микросхемы серии 1531 не так часто встречаются, можно воспользоваться зарубежными аналогами (а их можно выпаять из старых материнских плат). Всё это крепится прямо на модули SIMM.

Рисунок 5.

Если у Вас возникли новые вопросы или хотите что-нибудь добавить, то пишите на ящик

rona-soft@narod.ru или посетите страничку www.rona-soft.narod.ru.Весь материал собран из личного опыта...